# JOP Reference Handbook

# **JOP Reference Handbook**

Building Embedded Systems with a Java Processor

## **Martin Schoeberl**

#### Copyright © 2009 Martin Schoeberl

Martin Schoeberl Strausseng. 2-10/2/55 A-1050 Vienna, Austria

Email: martin@jopdesign.com

Visit the accompanying web site on http://www.jopdesign.com/ and

the JOP Wiki at http://www.jopwiki.com/

Published 2009 by CreateSpace,

http://www.createspace.com/

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, recording or otherwise, without the prior written permission of Martin Schoeberl.

#### **Library of Congress Cataloging-in-Publication Data**

Schoeberl, Martin

JOP Reference Handbook: Building Embedded Systems with a Java Processor / Martin Schoeberl Includes bibliographical references and index. ISBN 978-1438239699

Manufactured in the United States of America. Typeset in 11pt Times by Martin Schoeberl

## **Foreword**

This book is about JOP, the Java Optimized Processor. JOP is an implementation of the Java virtual machine (JVM) in hardware. The main implementation platform is a field-programmable gate array (FPGA). JOP began as a research project for a PhD thesis. In the mean time, JOP has been used in several industrial applications and as a research platform. JOP is a time-predictable processor for hard real-time systems implemented in Java.

JOP is open-source under the GNU GPL and has a growing user base. This book is written for all of you who build this lively community. For a long time the PhD thesis, some research papers, and the web site have been the main documentation for JOP. A PhD thesis focus is on research results and implementation details are usually omitted. This book complements the thesis and provides insight into the implementation of JOP and the accompanying JVM. Furthermore, it gives you an idea how to build an embedded real-time system based on JOP.

## **Acknowledgements**

Many users of JOP contributed to the design of JOP and to the tool chain. I also want to thank the students at the Vienna University of Technology during the four years of the course "The JVM in Hardware" and the students from CBS, Copenhagen at an embedded systems course in Java for the interesting questions and discussions. Furthermore, the questions and discussions in the Java processor mailing list provided valuable input for the documentation now available in form of this book. The following list of contributors to JOP is roughly in chronological order.

Ed Anuff wrote testmon.asm to perform a memory interface test and BlockGen.java to convert Altera .mif files to Xilinx memory blocks. Flavius Gruian wrote the initial version of JOPizer to generate the .jop file from the application classes. JOPizer is based on the open source library BCEL and is a substitute to the formerly used JavaCodeCompact from Sun. Peter Schrammel and Christof Pitter have implemented the first version of long bytecodes. Rasmus Pedersen based a class on very small information systems on JOP and invited my to co-teach this class in Copenhagen. During this time the first version of the WCET analysis tool was developed by Rasmus. Rasmus has also implemented an Eclipse plugin for the JOP design flow. Alexander Dejaco and Peter Hilber have developed the I/O interface board for the LEGO Mindstorms. Christof Pitter designed and implemented the chip-multiprocessor (CMP) version of JOP during his PhD thesis. Wolfgang Puffitsch first contribution to JOP was the finalization of the floating point library SoftFloat. Wolfgang, now an active developer of JOP, contributed several enhancements (e.g., exceptions, HW field access, data cache,...) and works towards real-time garbage collection for the CMP version of JOP. Alberto Andriotti contributed several JVM test cases. Stefan Hepp has implemented an optimizer at bytecode level during his Bachelor thesis work. Benedikt Huber has redesigned the WCET analysis tool for JOP during his Master's thesis. Trevor Harmon, who implemented the WCET tool Volta for JOP during his PhD thesis, helped me with proofreading of the handbook.

Furthermore, I would like to thank Walter Wilhelm from EEG for taking the risk to accept a JOP based hardware for the *Kippfahrleitung* project at a very early development stage of JOP. The development of JOP has received funding from the Wiener Innovationsföderprogram (Call IKT 2004) and from the EU project JEOPARD.

## **Contents**

| Fo | Foreword        |            |                                        |     |  |  |  |  |  |

|----|-----------------|------------|----------------------------------------|-----|--|--|--|--|--|

| Ac | know            | ledgem     | nents                                  | vii |  |  |  |  |  |

| 1  | Intro           | troduction |                                        |     |  |  |  |  |  |

|    | 1.1             | A Quio     | ck Tour on JOP                         | 1   |  |  |  |  |  |

|    |                 | 1.1.1      | Building JOP and Running "Hello World" | 1   |  |  |  |  |  |

|    |                 | 1.1.2      | The Design Structure                   | 2   |  |  |  |  |  |

|    | 1.2             | A Sho      | rt History                             |     |  |  |  |  |  |

|    | 1.3             | JOP F      | eatures                                | 4   |  |  |  |  |  |

|    | 1.4             | Is JOP     | the Solution for Your Problem?         | 6   |  |  |  |  |  |

|    | 1.5             | Outlin     | e of the Book                          | 6   |  |  |  |  |  |

| 2  | The Design Flow |            |                                        |     |  |  |  |  |  |

|    | 2.1             | Introdu    | uction                                 | 9   |  |  |  |  |  |

|    |                 | 2.1.1      | Tools                                  | 9   |  |  |  |  |  |

|    |                 | 2.1.2      | Getting Started                        | 10  |  |  |  |  |  |

|    |                 | 2.1.3      | Xilinx Spartan-3 Starter Kit           | 11  |  |  |  |  |  |

|    | 2.2             | Bootin     | ng JOP — How Your Application Starts   |     |  |  |  |  |  |

|    |                 | 2.2.1      | FPGA Configuration                     |     |  |  |  |  |  |

|    |                 | 2.2.2      | Java Download                          | 12  |  |  |  |  |  |

|    |                 | 2.2.3      | Combinations                           | 13  |  |  |  |  |  |

|    |                 | 2.2.4      | Stand Alone Configuration              | 14  |  |  |  |  |  |

|    | 2.3             | The D      | esign Flow                             | 15  |  |  |  |  |  |

|    |                 | 2.3.1      | Tools                                  | 15  |  |  |  |  |  |

|    |                 | 2.3.2      | Targets                                | 16  |  |  |  |  |  |

|    | 2.4             | Eclipse    | e                                      | 18  |  |  |  |  |  |

|    | 2.5             | Simula     | ation                                  | 19  |  |  |  |  |  |

|    |                 | 2.5.1      | JopSim Simulation                      | 19  |  |  |  |  |  |

|    |                 | 2.5.2      | VHDL Simulation                        | 20  |  |  |  |  |  |

X CONTENTS

| 2.6  | 71 <i>&amp;</i>                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2.7  | Information on the Web                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 2.8  | Porting JOP                                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.8.1 Test Utilities                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 2.9  | Extending JOP                                          | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.9.1 Native Methods                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.9.2 A new Peripheral Device                          | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.9.3 A Customized Instruction                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      |                                                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 2.10 | Directory Structure                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.10.1 The Java Sources for JOP                        | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 2.11 | The JOP Hello World Exercise                           | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.1 Manual build                                    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.2 Using make                                      | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.3 Change the Java Program                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.4 Change the Microcode                            | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.5 Use a Different Target Board                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.6 Compile a Different Java Application            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.7 Simulation                                      | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.11.8 WCET Analysis                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Java | and the Java Virtual Machine                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.1  | Java                                                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 3.1.1 History                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | •                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.2  |                                                        | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      |                                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | •                                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 3.2.3 Methods                                          | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      |                                                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.3  | Embedded Java                                          | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3.4  | Summary                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Hard | Iware Architecture                                     | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4.1  |                                                        | • <i>•</i><br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4.2  |                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| .=   |                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | 2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>3.1<br>3.2<br>4.1 | 2.7 Information on the Web 2.8 Porting JOP 2.8.1 Test Utilities 2.9 Extending JOP 2.9.1 Native Methods 2.9.2 A new Peripheral Device 2.9.3 A Customized Instruction 2.9.4 Dependencies and Configurations 2.10 Directory Structure 2.10.1 The Jov Hello World Exercise 2.11.1 Manual build 2.11.2 Using make 2.11.3 Change the Java Program 2.11.4 Change the Microcode 2.11.5 Use a Different Target Board 2.11.6 Compile a Different Java Application 2.11.7 Simulation 2.11.8 WCET Analysis  Java and the Java Virtual Machine 3.1 Java 3.1.1 History 3.1.2 The Java Programming Language 3.2 The Java Virtual Machine 3.2.1 Memory Areas 3.2.2 JVM Instruction Set 3.2.3 Methods 3.2.4 Implementation of the JVM 3.3 Embedded Java 3.4 Summary  Hardware Architecture 4.1 Overview of JOP 4.2 Microcode |  |  |  |

CONTENTS

|   |     | 4.2.2                       | Compact Microcode                                      | 1 |

|---|-----|-----------------------------|--------------------------------------------------------|---|

|   |     | 4.2.3                       | Instruction Set                                        | 2 |

|   |     | 4.2.4                       | Bytecode Example                                       | 3 |

|   |     | 4.2.5                       | Microcode Branches                                     | 4 |

|   |     | 4.2.6                       | Flexible Implementation of Bytecodes                   | 4 |

|   |     | 4.2.7                       | Summary                                                | 5 |

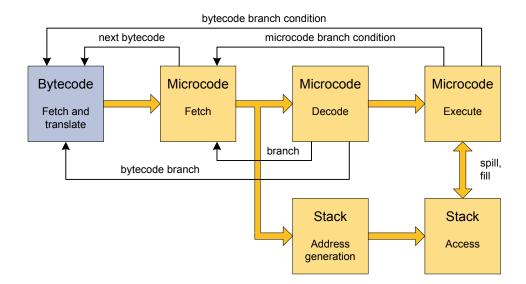

|   | 4.3 | The Pr                      | ocessor Pipeline                                       | 5 |

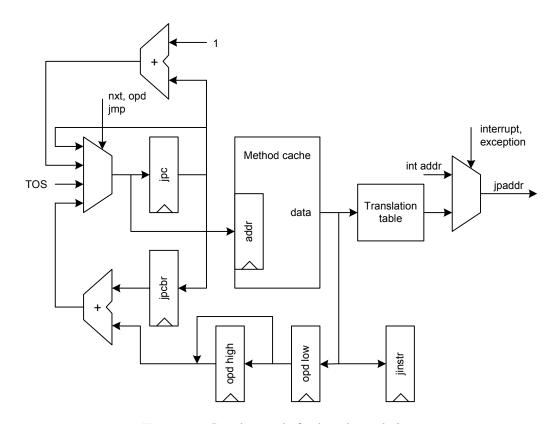

|   |     | 4.3.1                       | Java Bytecode Fetch                                    | 6 |

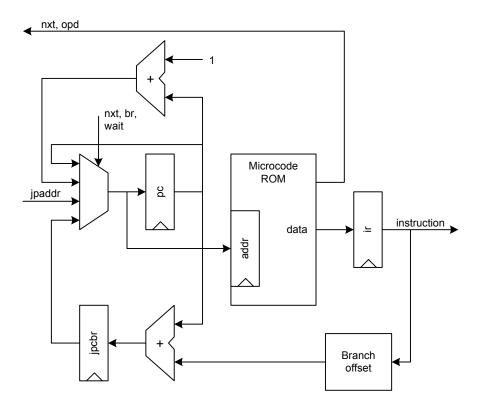

|   |     | 4.3.2                       | Microcode Instruction Fetch                            | 7 |

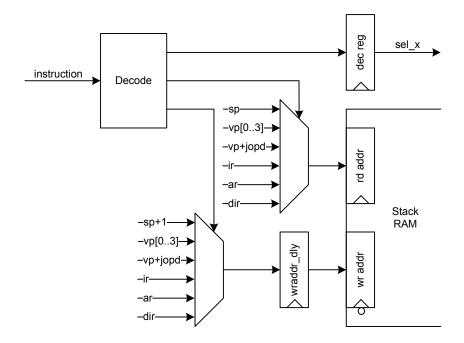

|   |     | 4.3.3                       | Decode and Address Generation                          | 9 |

|   |     | 4.3.4                       | Execute                                                | 0 |

|   |     | 4.3.5                       | Interrupt Logic 6                                      | 1 |

|   |     | 4.3.6                       | Summary                                                | 2 |

|   | 4.4 | The Sta                     | ack Cache                                              | 3 |

|   |     | 4.4.1                       | Java Computing Model 6.                                | 3 |

|   |     | 4.4.2                       | Access Patterns on the Java Stack 60                   | 6 |

|   |     | 4.4.3                       | JVM Stack Access Revised 6                             | 7 |

|   |     | 4.4.4                       | A Two-Level Stack Cache                                | 9 |

|   |     | 4.4.5                       | Summary                                                | 2 |

|   | 4.5 | The M                       | ethod Cache                                            | 3 |

|   |     | 4.5.1                       | Method Cache Architecture                              | 3 |

|   |     | 4.5.2                       | WCET Analysis                                          | 5 |

|   |     | 4.5.3                       | Caches Compared                                        | 7 |

|   |     | 4.5.4                       | Summary                                                | 9 |

| 5 | Dun | time Sy                     | stem 8                                                 | 4 |

| 5 | 5.1 | -                           | I-Time Profile for Embedded Java                       |   |

|   | 3.1 | 5.1.1                       | Application Structure                                  |   |

|   |     | 5.1.2                       | Threads                                                |   |

|   |     | 5.1.2                       | Scheduling                                             |   |

|   |     | 5.1.4                       | Memory                                                 |   |

|   |     | 5.1.5                       | Restrictions on Java                                   |   |

|   |     | 5.1.6                       | Interaction of RtThread, the Scheduler, and the JVM 8' |   |

|   |     | 5.1.7                       | Implementation Results                                 |   |

|   |     | 5.1.7                       |                                                        |   |

|   | 5.2 |                             | Summary                                                |   |

|   | 5.4 | 5.2.1                       | · · · · · · · · · · · · · · · · · · ·                  |   |

|   |     | $\mathcal{I}.\mathcal{L}.1$ | Introduction                                           | フ |

XII CONTENTS

|   |     | 5.2.2   | SCJ Level 1                                                      |

|---|-----|---------|------------------------------------------------------------------|

|   | 5.3 | JVM A   | rchitecture                                                      |

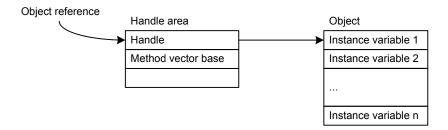

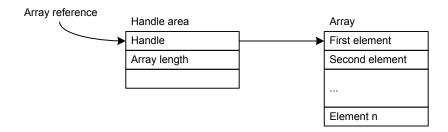

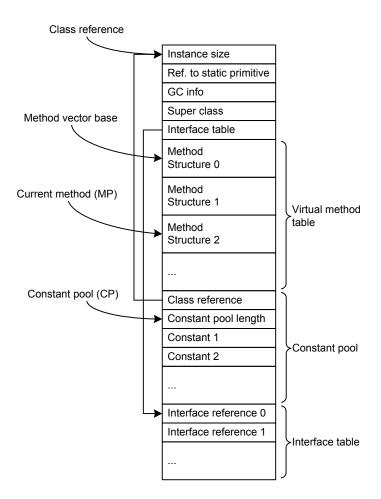

|   |     | 5.3.1   | Runtime Data Structures                                          |

|   |     | 5.3.2   | Class Initialization                                             |

|   |     | 5.3.3   | Synchronization                                                  |

|   |     | 5.3.4   | Booting the JVM                                                  |

| 6 | Wor | st-Case | Execution Time 103                                               |

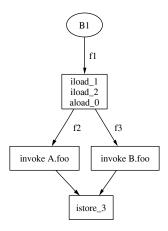

| • | 6.1 |         | ode WCET Analysis                                                |

|   |     | 6.1.1   | Microcode Path Analysis                                          |

|   |     | 6.1.2   | Microcode Low-level Analysis                                     |

|   |     | 6.1.3   | Bytecode Independency                                            |

|   |     | 6.1.4   | WCET of Bytecodes                                                |

|   | 6.2 | WCET    | Analysis of the Java Application                                 |

|   |     | 6.2.1   | High-Level WCET Analysis                                         |

|   |     | 6.2.2   | WCET Annotations                                                 |

|   |     | 6.2.3   | ILP Formulation                                                  |

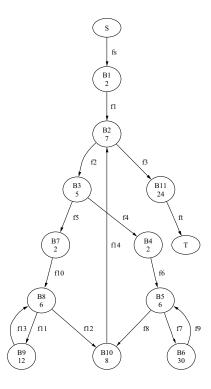

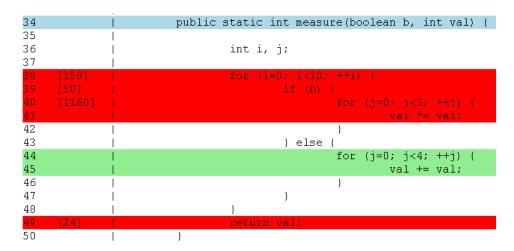

|   |     | 6.2.4   | An Example                                                       |

|   |     | 6.2.5   | Dynamic Method Dispatch                                          |

|   |     | 6.2.6   | Cache Analysis                                                   |

|   |     | 6.2.7   | WCET Analyzer                                                    |

|   | 6.3 | Evalua  | tion                                                             |

|   |     | 6.3.1   | Benchmarks                                                       |

|   |     | 6.3.2   | Analysis and Measurements                                        |

|   | 6.4 | Discuss | sion                                                             |

|   |     | 6.4.1   | On Correctness of WCET Analysis                                  |

|   |     | 6.4.2   | Is JOP the Only Target Architecture?                             |

|   |     | 6.4.3   | Object-oriented Evaluation Examples                              |

|   |     | 6.4.4   | WCET Analysis for Chip-multiprocessors                           |

|   |     | 6.4.5   | Co-Development of Processor Architecture and WCET Analysis $128$ |

|   |     | 6.4.6   | Further Paths to Explore                                         |

|   | 6.5 | Summa   | ,                                                                |

|   | 6.6 |         | Reading                                                          |

|   |     | 6.6.1   | WCET Analysis                                                    |

|   |     | 6.6.2   | WCET Analysis for Java                                           |

|   |     | 6.6.3   | WCET Analysis for JOP                                            |

CONTENTS

| 7 | Real | l-Time G   | Sarbage Collection            | 133   |

|---|------|------------|-------------------------------|-------|

|   | 7.1  | Introdu    | action                        | . 133 |

|   |      | 7.1.1      | Incremental Collection        | . 135 |

|   |      | 7.1.2      | Conservatism                  | . 135 |

|   |      | 7.1.3      | Safety Critical Java          | . 135 |

|   | 7.2  | Schedu     | uling of the Collector Thread | . 136 |

|   |      | 7.2.1      | An Example                    | . 137 |

|   |      | 7.2.2      | Minimum Heap Size             | . 139 |

|   |      | 7.2.3      | Garbage Collection Period     | . 143 |

|   | 7.3  | SCJ Si     | mplifications                 |       |

|   |      | 7.3.1      | Simple Root Scanning          | . 149 |

|   |      | 7.3.2      | Static Memory                 |       |

|   | 7.4  | Implen     | nentation                     |       |

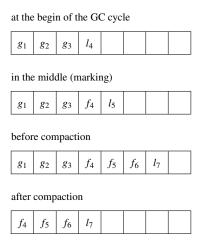

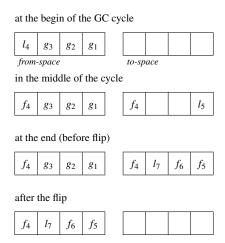

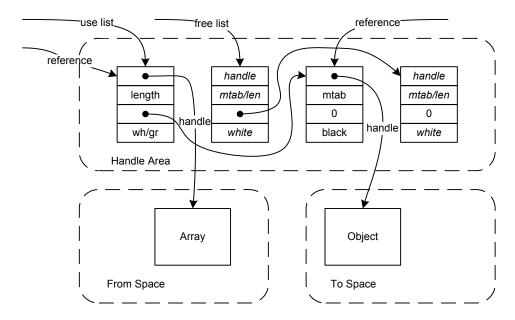

|   |      | 7.4.1      | Heap Layout                   | . 152 |

|   |      | 7.4.2      | The Collector                 | . 153 |

|   |      | 7.4.3      | The Mutator                   | . 157 |

|   | 7.5  | Evalua     | tion                          | . 161 |

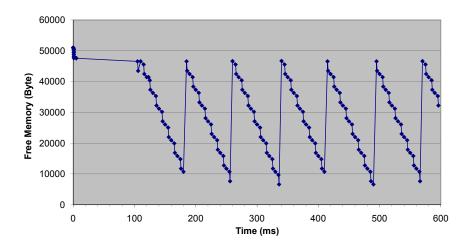

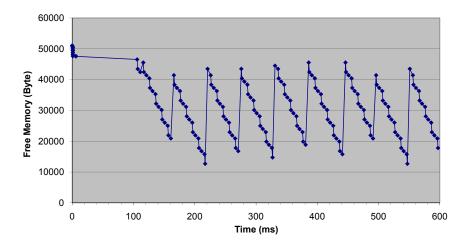

|   |      | 7.5.1      | Scheduling Experiments        | . 162 |

|   |      | 7.5.2      | Measuring Release Jitter      |       |

|   |      | 7.5.3      | Measurements                  |       |

|   |      | 7.5.4      | Discussion                    |       |

|   | 7.6  | Analys     | sis                           |       |

|   |      | 7.6.1      | Worst Case Memory Consumption |       |

|   |      | 7.6.2      | WCET of the Collector         |       |

|   | 7.7  | Summa      | ary                           |       |

|   | 7.8  |            | Reading                       |       |

| 8 | Low  | -level I/C | 0                             | 177   |

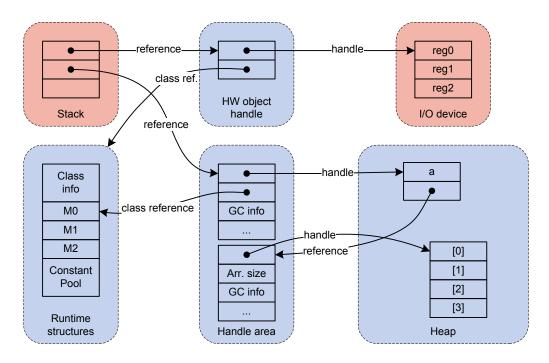

|   | 8.1  | Hardw      | are Objects                   | . 177 |

|   |      | 8.1.1      | An Example                    | . 177 |

|   |      | 8.1.2      | Definition                    | . 179 |

|   |      | 8.1.3      | Access Control                | . 180 |

|   |      | 8.1.4      | Using Hardware Objects        | . 182 |

|   |      | 8.1.5      | Hardware Arrays               |       |

|   |      | 8.1.6      | Garbage Collection            |       |

|   |      | 8.1.7      | Hardware Object Creation      |       |

|   |      | 8.1.8      | Board Configurations          |       |

XIV CONTENTS

|    |       | 8.1.9   | Implementation                           |

|----|-------|---------|------------------------------------------|

|    |       | 8.1.10  | Legacy Code                              |

|    | 8.2   | Interru | pt Handlers                              |

|    |       | 8.2.1   | Synchronization                          |

|    |       | 8.2.2   | Interrupt Handler Registration           |

|    |       | 8.2.3   | Implementation                           |

|    |       | 8.2.4   | An Example                               |

|    | 8.3   | Standa  | rd Devices                               |

|    |       | 8.3.1   | The System Device                        |

|    |       | 8.3.2   | The UART                                 |

| 9  | The 9 | SimpCo  | on Interconnect 197                      |

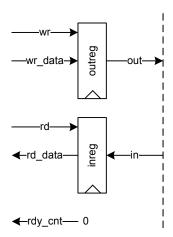

| •  | 9.1   | -       | action                                   |

|    |       | 9.1.1   | Features                                 |

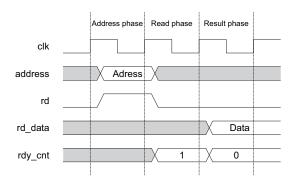

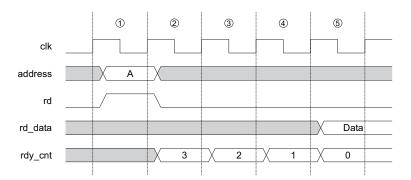

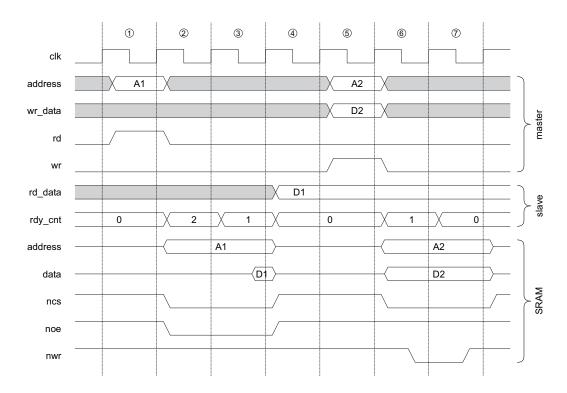

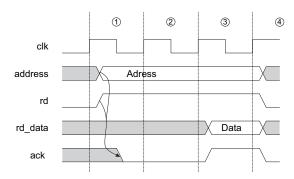

|    |       | 9.1.2   | Basic Read Transaction                   |

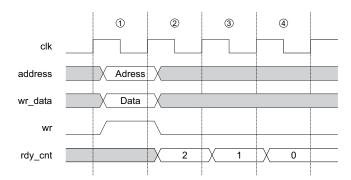

|    |       | 9.1.3   | Basic Write Transaction                  |

|    | 9.2   | SimpC   | on Signals                               |

|    |       | 9.2.1   | Master Signal Details                    |

|    |       | 9.2.2   | Slave Signal Details                     |

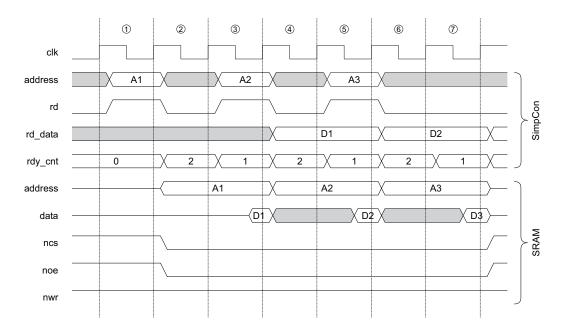

|    | 9.3   | Slave A | Acknowledge                              |

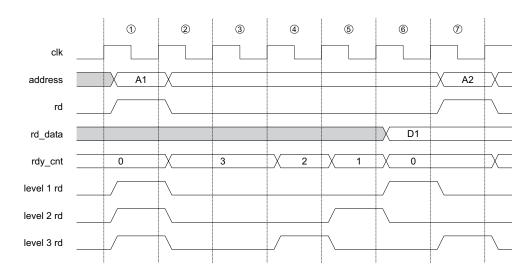

|    | 9.4   | Pipelin | ing                                      |

|    | 9.5   | Interco | nnect                                    |

|    | 9.6   | Examp   | les                                      |

|    |       | 9.6.1   | I/O Port                                 |

|    |       | 9.6.2   | SRAM interface                           |

|    | 9.7   |         | ble VHDL Files                           |

|    |       | 9.7.1   | Components                               |

|    |       | 9.7.2   | Bridges                                  |

|    | 9.8   | •       | New Interconnection Standard?            |

|    |       | 9.8.1   | Common SoC Interconnections              |

|    |       | 9.8.2   | What's Wrong with the Classic Standards? |

|    |       | 9.8.3   | Evaluation                               |

|    | 9.9   | Summa   | ary                                      |

| 10 | Chip  | Multip  | rocessing 217                            |

|    | _     | _       | ry Arbitration                           |

|    |       | 10 1 1  | Main Memory 217                          |

CONTENTS XV

|    |       | 10.1.2 I/O Devices       218         Booting a CMP System       218         CMP Scheduling       219         10.3.1 One Thread per Core       220         10.3.2 Scheduling on the CMP System       220 |

|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | Evalu | uation 225                                                                                                                                                                                              |

|    | 11.1  | Hardware Platforms                                                                                                                                                                                      |

|    | 11.2  | Chip Area and Clock Frequency                                                                                                                                                                           |

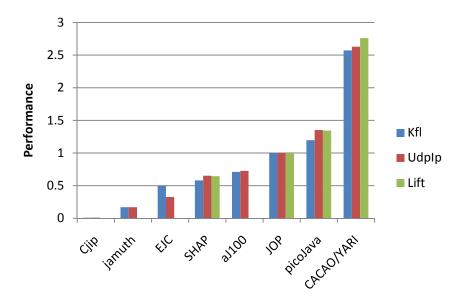

|    | 11.3  | Performance                                                                                                                                                                                             |

|    | 11.4  | Applications                                                                                                                                                                                            |

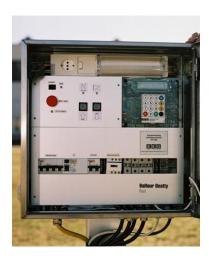

|    |       | 11.4.1 The Kippfahrleitung                                                                                                                                                                              |

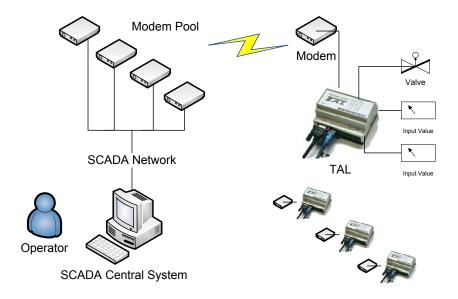

|    |       | 11.4.2 The SCADA Device TeleAlarm                                                                                                                                                                       |

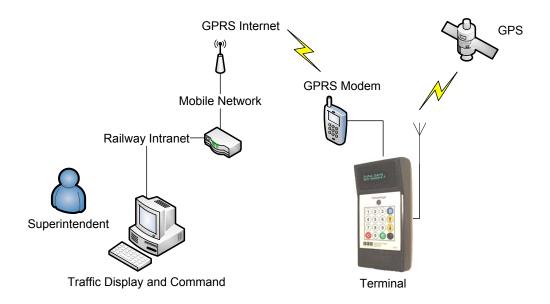

|    |       | 11.4.3 Support for Single Track Railway Control                                                                                                                                                         |

|    |       | 11.4.4 Communication and Common Design Patterns                                                                                                                                                         |

|    |       | 11.4.5 Discussion                                                                                                                                                                                       |

|    | 11.5  | Summary                                                                                                                                                                                                 |

| 10 | Dalai | and Marula                                                                                                                                                                                              |

| 12 |       | red Work 24                                                                                                                                                                                             |

|    | 12.1  | Java Coprocessors                                                                                                                                                                                       |

|    | 12.2  | Java Processors                                                                                                                                                                                         |

|    | 12.2  | 12.2.1 picoJava                                                                                                                                                                                         |

|    |       | 12.2.2 aJile JEMCore                                                                                                                                                                                    |

|    |       | 12.2.3 Cjip                                                                                                                                                                                             |

|    |       | 12.2.4 Lightfoot                                                                                                                                                                                        |

|    |       | 12.2.5 LayaCORE                                                                                                                                                                                         |

|    |       | 12.2.6 Komodo, jamuth                                                                                                                                                                                   |

|    |       | 12.2.7 FemtoJava                                                                                                                                                                                        |

|    |       | 12.2.8 jHISC                                                                                                                                                                                            |

|    |       | 12.2.9 SHAP                                                                                                                                                                                             |

|    |       | 12.2.10 Azul                                                                                                                                                                                            |

|    |       |                                                                                                                                                                                                         |

| 13 | Sum   | mary 25                                                                                                                                                                                                 |

|    |       | A Real-Time Java Processor                                                                                                                                                                              |

|    | 13.2  | A Resource-Constrained Processor                                                                                                                                                                        |

|    | 13.3  | Future Work                                                                                                                                                                                             |

XVI CONTENTS

| Α   | Publications |                     |     |  |  |  |  |  |

|-----|--------------|---------------------|-----|--|--|--|--|--|

| В   | Acronyms     |                     |     |  |  |  |  |  |

| С   | JOP          | Instruction Set     | 267 |  |  |  |  |  |

| D   | Byte         | code Execution Time | 297 |  |  |  |  |  |

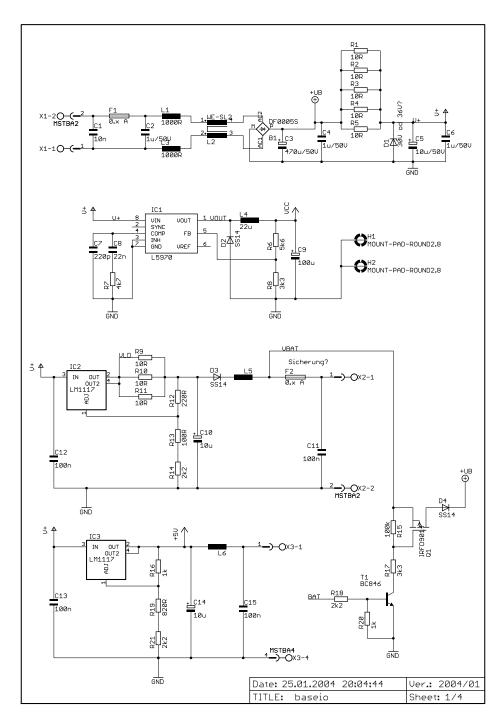

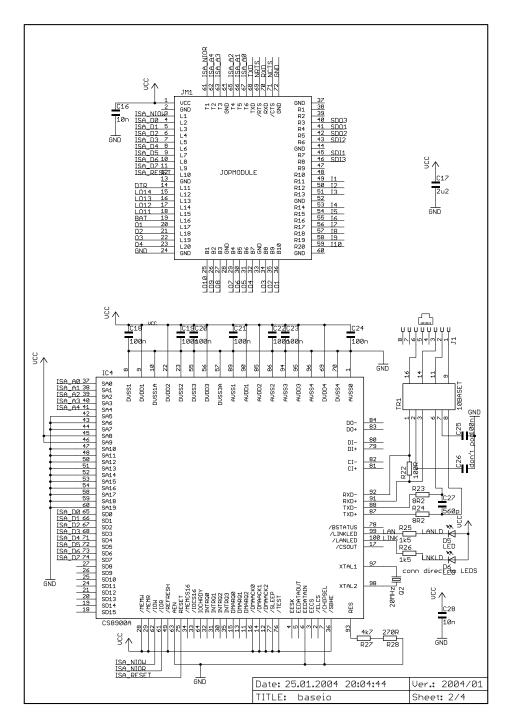

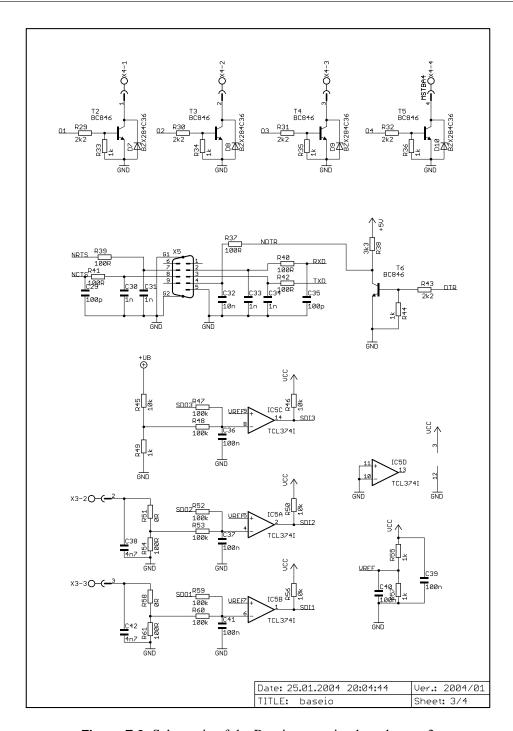

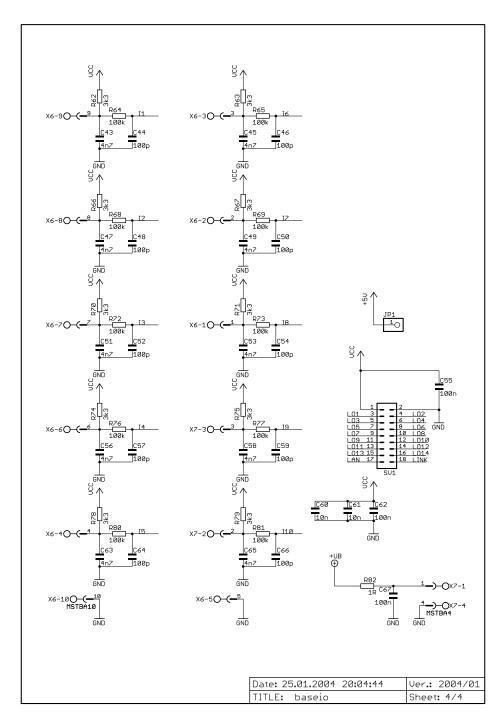

| Ε   | Print        | ted Circuit Boards  | 309 |  |  |  |  |  |

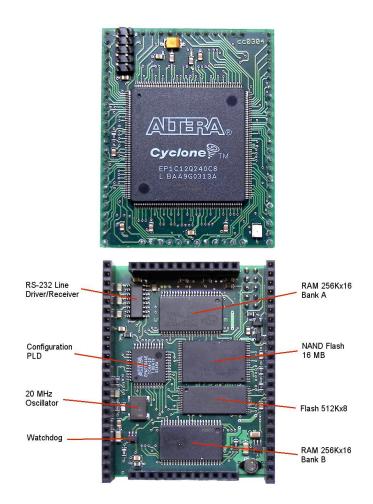

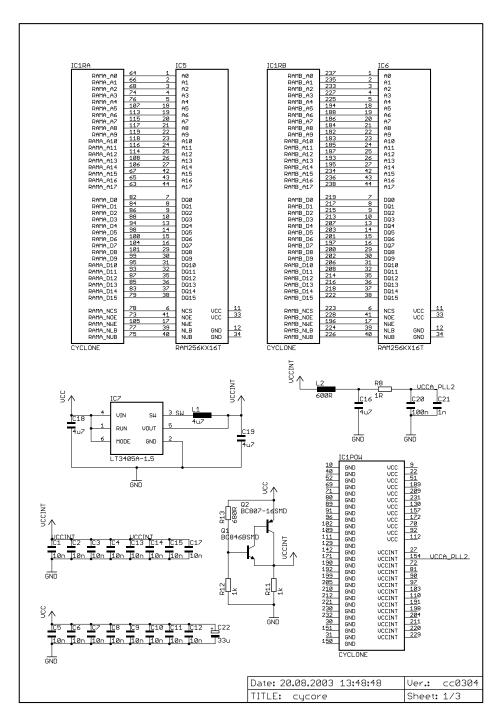

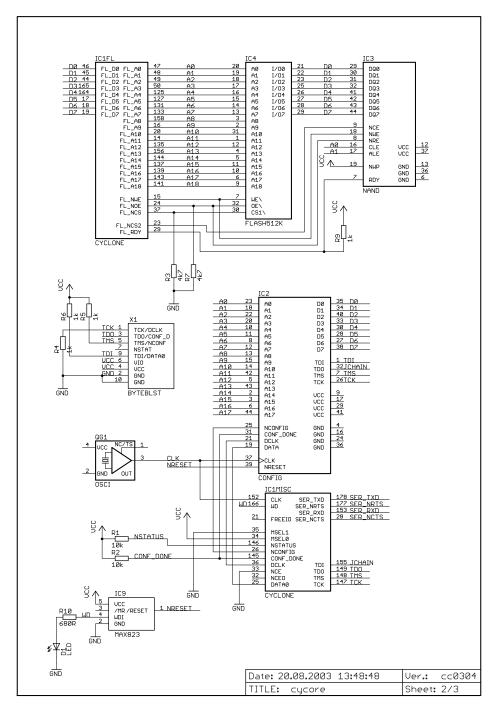

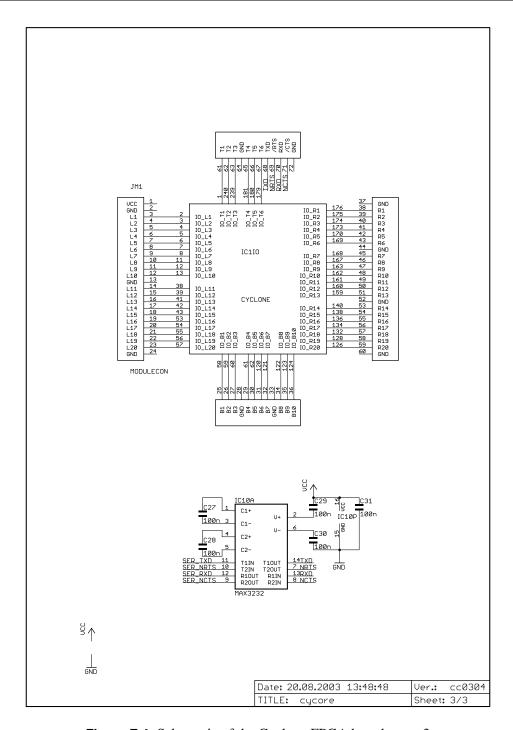

|     | E.1          | Cyclone FPGA Board  | 310 |  |  |  |  |  |

|     | E.2          | Baseio Board        | 314 |  |  |  |  |  |

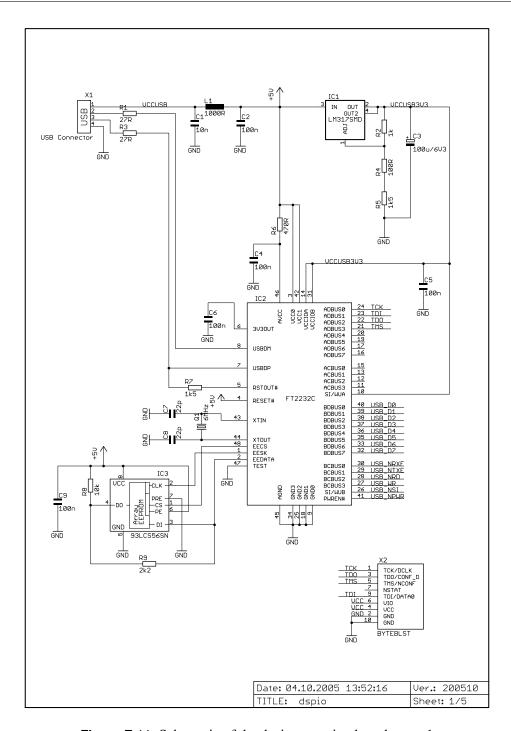

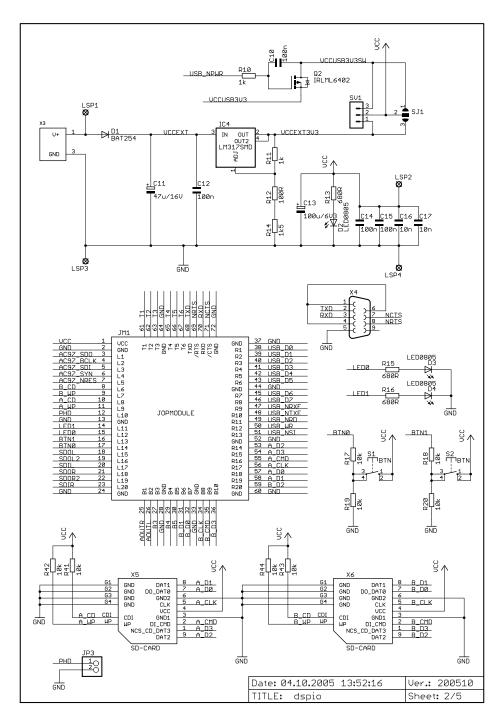

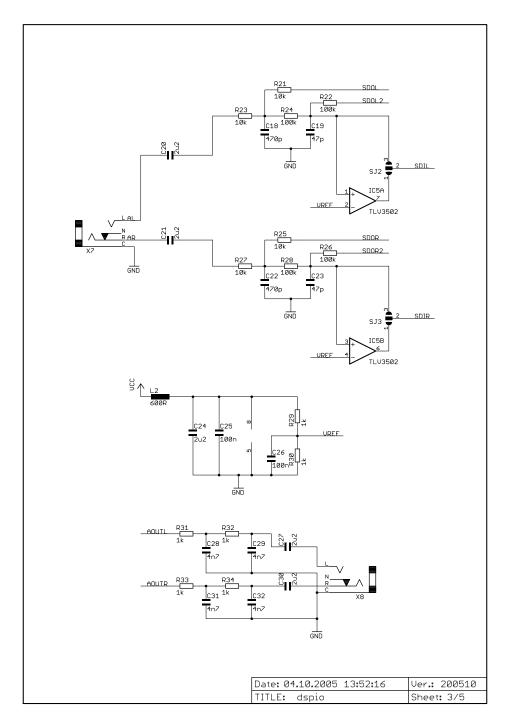

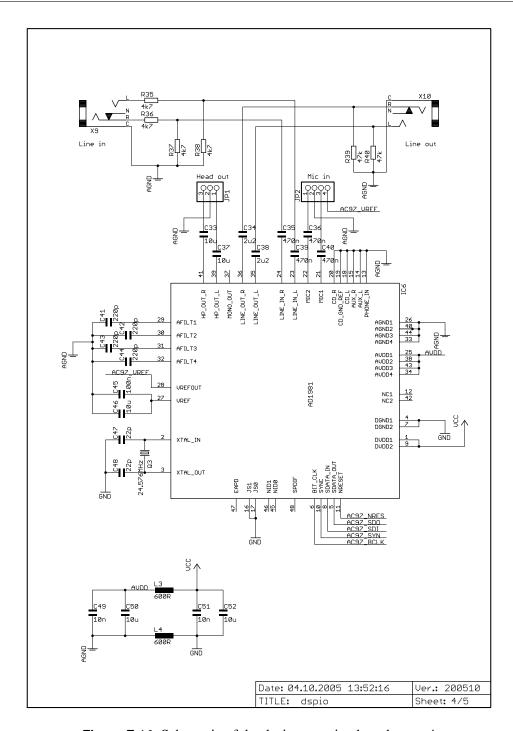

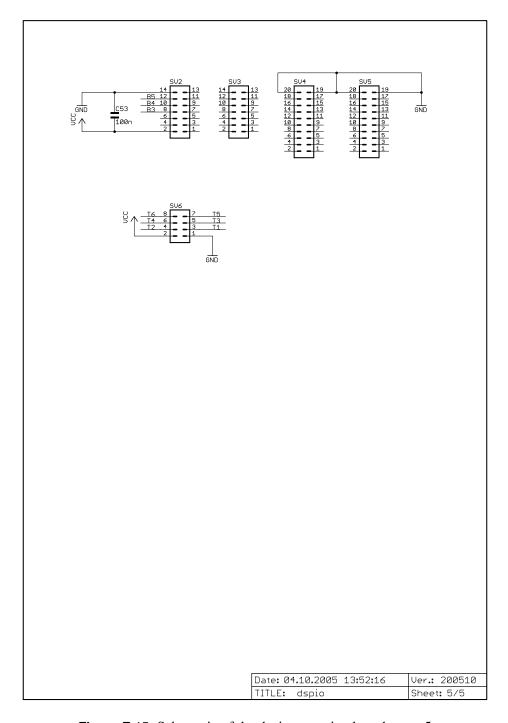

|     | E.3          | Dspio Board         | 319 |  |  |  |  |  |

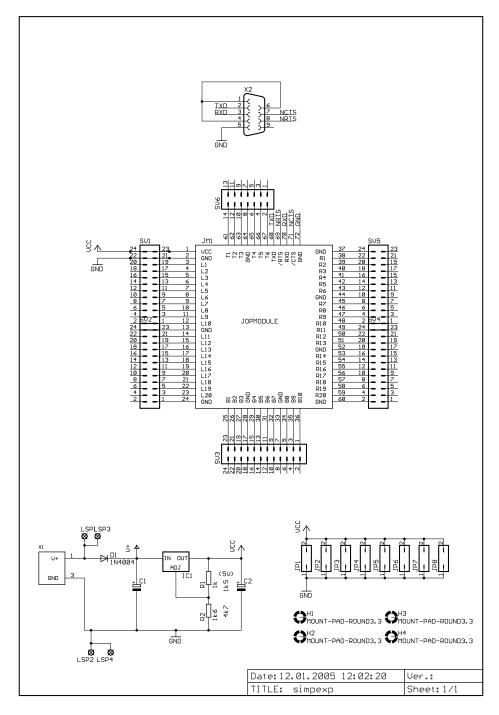

|     | E.4          |                     |     |  |  |  |  |  |

| Bil | bliogr       | aphy                | 327 |  |  |  |  |  |

| Inc | dex          |                     | 343 |  |  |  |  |  |

## 1 Introduction

This handbook introduces a Java processor for embedded real-time systems, in particular the design of a small processor for resource-constrained devices with time-predictable execution of Java programs. This Java processor is called JOP – which stands for Java Optimized Processor –, based on the assumption that a full native implementation of all Java bytecode instructions is not a useful approach.

#### 1.1 A Quick Tour on JOP

In the following section we will give a quick overview on JOP and a short description how to get JOP running within an FPGA. A detailed description of the build process can be found in Chapter 2. JOP is a soft-core written in VHDL plus tools in Java, a simplified Java library (JDK), and application examples. JOP is delivered in source only.

## 1.1.1 Building JOP and Running "Hello World"

To build JOP you first have to download the source tree. A *Makefile* (or an Ant file) contains all necessary steps to build the tools, the processor, and the application. Configuration of the FPGA and downloading the Java application is also part of the Makefile.

In this description we assume the FPGA board Cycore (see Appendix E.1). This board is the default target for the Makefile. The board has to be connected to the power supply and to the PC via a ByteBlaster download cable and a serial cable.

The FPGA is configured via the ByteBlaster cable. The Java application is downloaded after the FPGA configuration via the serial cable. Besides the download the serial cable is also used as a communication link between JOP and the PC. System.out and System.in represent this serial link on JOP.

In order to build the whole system you need a Java compiler<sup>1</sup> and an FPGA compiler. In our case we use the free web edition of Quartus from Altera.<sup>2</sup> As we use make and

<sup>&</sup>lt;sup>1</sup>Download the Java SE Development Kit (JDK) from http://java.sun.com/javase/downloads/index.jsp.

<sup>2</sup>http://www.altera.com/

2 1 Introduction

the preprocessor from the GNU compiler collection, Cygwin<sup>3</sup> should be installed under Windows.

When all tools are setup correctly<sup>4</sup> a simple make should build the tools, the processor, compile the "Hello World" example, configure the FPGA and download the application. The whole build process will take a few minutes. After typing

make

you see a lot of messages from the various tools. However, the last lines should be actual messages received from JOP. It should look similar to the following:

JOP start V 20080821 60 MHz, 1024 KB RAM, 1 CPUs Hello World from JOP!

Note that JOP prints some internal information, such as version and memory size, at startup. After that, the message "Hello World from JOP!" can be seen. Our first program runs on JOP!

As a next step, locate the Hello World example in the source tree<sup>5</sup> and change the output message. The tools and the processor have been built already. So we do not need to compile everything from scratch. Use the following make target to just compile the Java application and download the processor and the application:

make japp

JVM exit!

The compile process should now be faster and the output similar to before.

The Hello World application is the default target in the Makefile. See Chapter 2 for a description how this target can be changed. In case you use a different FPGA board you can find information on how to change the build process also in Chapter 2.

### 1.1.2 The Design Structure

Browsing the source tree of JOP can give the impression that the design is complex. However, the basic structure is not that complex. The design consists of three entities:

#### 1. The processor JOP

<sup>3</sup>http://www.cygwin.com/

<sup>&</sup>lt;sup>4</sup>Check at the command prompt that javac is in the path.

<sup>&</sup>lt;sup>5</sup>.../iop/java/target/src/test/test/HelloWorld.java

1.2 A SHORT HISTORY 3

- 2. Supporting tools

- 3. The Java library and applications

The different entities are also reflected during the configuration and download process. The download is a two step process:

- Configuration of the FPGA: JOP is downloaded via a FPGA download cable (e.g., ByteBlaster on the PCs parallel port). After FPGA configuration the processor automatically starts and listens to the second channel (the serial line) for the software download.

- Java application download: the compiled and linked application is downloaded usually via a serial line. JOP stores the application in the main memory and starts execution at main() after the download.

Further details of the source structure can be found in Section 2.10.

## 1.2 A Short History

The first version of JOP was created in 2000 based on the adaptation of earlier processor designs created between 1995 and 2000. The first version was written in Altera's proprietary AHDL language. The first *program* (3 bytecode instructions) ran on JOP on October 2, 2000. The first approach was a general purpose accumulator/register machine with 16-bit instructions, 32-bit registers, and a pipeline length of 3. It used the on-chip block memory to implement (somehow unusual) 1024 registers.

The JVM was implemented in the assembler of that machine. That concept was similar to the microcode in the current JOP version. The decoding of the bytecode was performed by a long jump table. In the best case (assuming a local, single cycle memory) a simple bytecode (e.g. iadd) took 12 cycles for fetch and decode and additional 11 cycles for execution.

A redesign followed in April 2001, now coded in VHDL. The second version of JOP introduced features to speed up the implementation of the JVM with specific instructions for the stack access and a dedicated stack pointer. The register file was reduced to 16 entries and the instruction width reduced to 8 bits. The pipeline contained 5 stages and special support for decoding bytecode instructions was added – a first version of the dynamic bytecode to microcode address translation as it is used in the current version of JOP. The enhancements within JOP2 resulted in the reduction of the execution time for a simple bytecode to 3 cycles. A great enhancement, compared to the 23 cycles in JOP1.

4 1 Introduction

The next redesign (JOP3) followed in June 2001. The challenge was to execute simple bytecodes fully pipelined in a single cycle. The microcode instruction set was changed to implement a stack machine and the execution stage combined with the on-chip stack cache. Microcode instructions where coded in 16 bit and the pipeline was reduced to four stages. JOP3 is the basis of JOP as it is described in this handbook. The later changes have not been so radical to call them a redesign.

The first real-world application of JOP was in the project *Kippfahrleitung* (see Section 11.4.1). At the start of the project (October 2001) JOP could only execute a single static method stored in the on-chip memory. The project greatly pushed the development of JOP. After successful deployment of the JOP-based control system in the field, several projects followed (TeleAlarm, Lift, the railway control system). The source of the commercial applications is part of the JOP distribution. Some of these applications are now used as a test bench for embedded Java performance and to benchmark WCET analysis tools.

More details and the source code of JOP1<sup>6</sup>, JOP2<sup>7</sup> and the first JOP3<sup>8</sup> version are available on the web site.

#### 1.3 JOP Features

This book presents a hardware implementation of the Java virtual machine (JVM), targeting small embedded systems with real-time constraints. JOP is designed from the ground up with time-predictable execution of Java bytecode as a major design goal. All functional units, and especially the interactions between them, are carefully designed to avoid any time dependency between bytecodes.

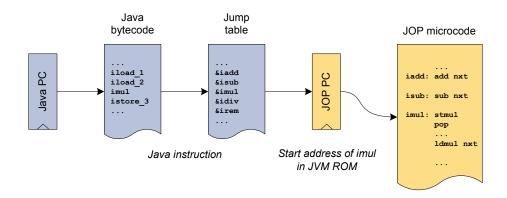

JOP is a stack computer with its own instruction set, called microcode in this book. Java bytecodes are translated into microcode instructions or sequences of microcode. The difference between the JVM and JOP is best described as the following:

The JVM is a CISC stack architecture, whereas JOP is a RISC stack architecture.

The architectural features and highlights of JOP are:

• Dynamic translation of the CISC Java bytecodes to a RISC, stack based instruction set (the microcode) that can be executed in a 3 stage pipeline.

<sup>6</sup>http://www.jopdesign.com/jop1.jsp

<sup>&</sup>lt;sup>7</sup>http://www.jopdesign.com/jop2.jsp

<sup>8</sup>http://www.jopdesign.com/jop3.jsp

1.3 JOP FEATURES 5

• The translation takes exactly one cycle per bytecode and is therefore pipelined. Compared to other forms of dynamic code translation the translation does not add any variable latency to the execution time and is therefore time predictable.

- Interrupts are inserted in the translation stage as special bytecodes and are transparent to the microcode pipeline.

- The short pipeline (4 stages) results in short conditional branch delays and a hard to analyze branch prediction logic or branch target buffer can be avoided.

- Simple execution stage with the two topmost stack elements as discrete registers. No write back stage or forwarding logic is needed.

- Constant execution time (one cycle) for all microcode instructions. The microcode pipeline never stalls. Loads and stores of object fields are handled explicitly.

- No time dependencies between bytecodes result in a simple processor model for the low-level WCET analysis.

- Time predictable instruction cache that caches whole methods. Only invoke and return instruction can result in a cache miss. All other instructions are guaranteed cache hits.

- Time predictable data cache for local variables and the operand stack. Access to local

variables is a guaranteed hit and no pipeline stall can happen. Stack cache fill and

spill is under microcode control and analyzable.

- No prefetch buffers or store buffers that can introduce unbounded time dependencies

of instructions. Even simple processors can contain an instruction prefetch buffer that

prohibits exact WCET values. The design of the method cache and the translation unit

avoids the variable latency of a prefetch buffer.

- Good average case performance compared with other non real-time Java processors.

- Avoidance of hard to analyze architectural features results in a very small design. Therefore an available real estate can be used for a chip multi-processor solution.

- JOP is the smallest hardware implementation of the JVM available to date. This fact

enables usage of low-cost FPGAs in embedded systems. The resource usage of JOP

can be configured to trade size against performance for different application domains.

6 1 Introduction

• JOP is actually in use in several real-world applications showing that a Java based embedded system implemented in an FPGA is a viable option.

JOP is implemented as a soft-core in a field programmable gate array (FPGA) giving a lot of flexibility for the overall hardware design. The processor can easily be extended by peripheral components inside the same chip. Therefore, it is possible to customize the solution exactly to the needs of the system.

#### 1.4 Is JOP the Solution for Your Problem?

I had a lot of fun, and still have, developing and using JOP. However, should you use JOP? JOP is a processor design intended as a time predictable solution for hard real-time systems. If your application or research focus is on those systems and you prefer Java as programming language, JOP is the right choice. If you are interested in larger, dynamic systems, JOP is the wrong choice. If average performance is important for you and you do not care about worst-case performance other solutions will probably do a better job.

#### 1.5 Outline of the Book

Chapter 2 gives a detailed introduction into the design flow of JOP. It explains how the individual parts are compiled and which files have to be changed when you want to extend JOP or adapt it to a new hardware platform. The chapter is concluded by an exercise to explore the different steps in the design flow.

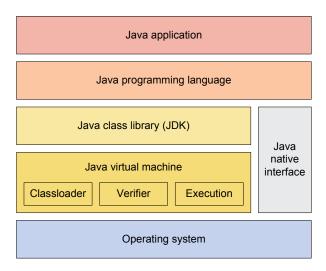

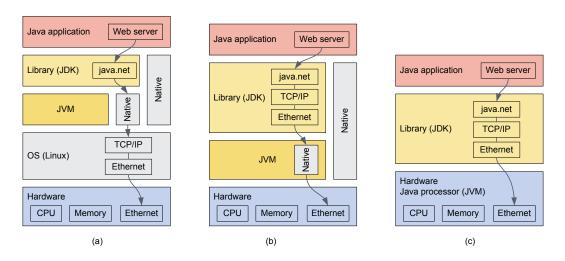

Chapter 3 provides background information on the Java programming language, the execution environment, and the Java virtual machine, for Java applications. If you are already familiar with Java and the JVM, feel free to skip this chapter.

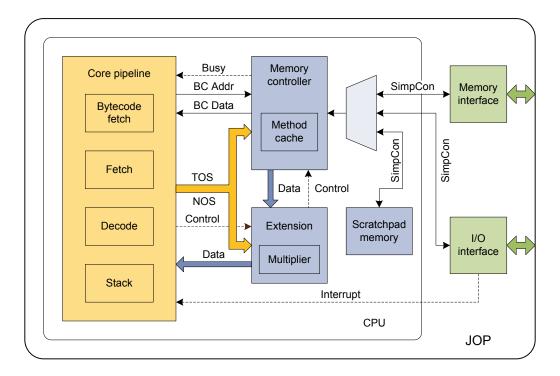

Chapter 4 is the main chapter in which the architecture of JOP is described. The motivation behind different design decisions is given. A Java processor alone is not a complete JVM. Chapter 5 describes the runtime environment on top of JOP, including the definition of a real-time profile for Java and the description of the scheduler in Java.

In Chapter 6 worst-case execution time (WCET) analysis for JOP is presented. It is shown how the time-predictable bytecode instructions form the basis of WCET analysis of Java applications.

Garbage collection (GC) is an important part of the Java technology. Even in real-time systems new real-time garbage collectors emerge. In Chapter 7 the formulas to calculate

the correct scheduling of the GC thread are given and the implementation of the real-time GC for JOP is explained.

JOP uses a simple and efficient system-on-chip interconnection called SimpCon to connect the memory controller and peripheral devices to the processor pipeline. The definition of SimpCon and the rationale behind the SimpCon specification is given in Chapter 9. Based on a SimpCon memory arbiter, chip-multiprocessor (CMP) versions of JOP can be configured. Chapter 10 gives some background information on the JOP CMP system.

In Chapter 11, JOP is evaluated with respect to size and performance. This is followed by a description of some commercial real-world applications of JOP. Other hardware implementations of the JVM are presented in Chapter 12. Different hardware solutions from both academia and industry for accelerating Java in embedded systems are analyzed.

Finally, in Chapter 13, the work is summarized and the major contributions are presented. This chapter concludes with directions for future work using JOP and real-time Java. A more theoretical treatment of the design of JOP can be found in the PhD thesis [123], which is also available as book [131].

## 2 The Design Flow

This chapter describes the design flow for JOP — how to build the Java processor and a Java application from scratch (the VHDL and Java sources) and download the processor to an FPGA and the Java application to the processor.

#### 2.1 Introduction

JOP [123], the Java optimized processor, is an open-source development platform available for different targets (Altera and Xilinx FPGAs and various types of FPGA boards). To support several targets, the resulting design-flow is a little bit complicated. There is a Makefile available and when everything is set up correctly, a simple

make

should build everything from the sources and download a *Hello World* example. However, to customize the Makefile for a different target it is necessary to understand the complete design flow. It should be noted that an Ant<sup>1</sup> based build process is also available.

#### 2.1.1 Tools

All needed tools are freely available.

- Java SE Development Kit (JDK) Java compiler and runtime

- Cygwin GNU tools for Windows. Packages cvs, gcc and make are needed

- Quarts II Web Edition VHDL synthesis, place and route for Altera FPGAs

The PATH variable should contain entries to the executables of all packages (java and javac, Cygwin bin, and Quartus executables). Check the PATH at the command prompt with:

<sup>1</sup>http://ant.apache.org/

10 2 THE DESIGN FLOW

```

javac

gcc

make

git

quartus_map

```

All the executables should be found and usually report their usage.

#### 2.1.2 Getting Started

This section shows a quick step-by-step build of JOP for the Cyclone target in the minimal configuration. All directory paths are given relative to the JOP root directory jop. The build process is explained in more detail in one of the following sections.

#### **Download the Source**

Create a working directory and download JOP from the GIT server:

```

git clone git: //www.soc.tuwien.ac.at/jop.git

```

For a write access clone (for developers) use following URL:

```

git clone ssh://user@www.soc.tuwien.ac.at/home/git/jop.git

```

All sources are downloaded to a directory jop. For the following command change to this directory. Create the needed directories with:

make directories

#### **Tools**

The tools contain Jopa, the microcode assembler, JopSim, a Java based simulation of JOP, and JOPizer, the application builder. The tools are built with following make command:

make tools

#### Assemble the Microcode JVM, Compile the Processor

The JVM configured to download the Java application from the serial interface is built with: make jopser

This command also invokes Quartus to build the processer. If you want to build it within Quartus follow the following instructions:

2.1 Introduction 11

1. Start Quartus II and open the project jop.qpf from directory quartus/cycmin in Quartus with *File – Open Project...*.

- 2. Start the compiler and fitter with *Processing Start Compilation*.

- 3. After successful compilation the FPGA is configured with *Tools Programmer* and *Start*.

#### Compiling and Downloading the Java Application

A simple *Hello World* application is the default application in the Makefile. It is built and downloaded to JOP with:

```

make japp

```

The "Hello World" message should be printed in the command window.

For a different application change the Makefile targets or override the make variables at the command line. The following example builds and runs some benchmarks on JOP:

```

make japp -e P1=bench P2=jbe P3=DoAll

```

The three variables P1, P2, and P3 are a shortcut to set the directory, the package name, and the main class of the application.

#### **USB** based Boards

Several Altera based boards use an FTDI FT2232 USB chip for the FPGA and Java program download. To change the download flow for those boards change the value of the following variable in the Makefile to true:

```

USB=true

```

The Java download channel is mapped to a virtual serial port on the PC. Check the port number in the system properties and set the variable COM\_PORT accordingly.

### 2.1.3 Xilinx Spartan-3 Starter Kit

The Xilinx tool chain is still not well supported by the Makefile or the Ant design flow. Here is a short list on how to build JOP for a Xilinx board:

```

make tools

cd asm

jopser

cd ..

```

12 2 THE DESIGN FLOW